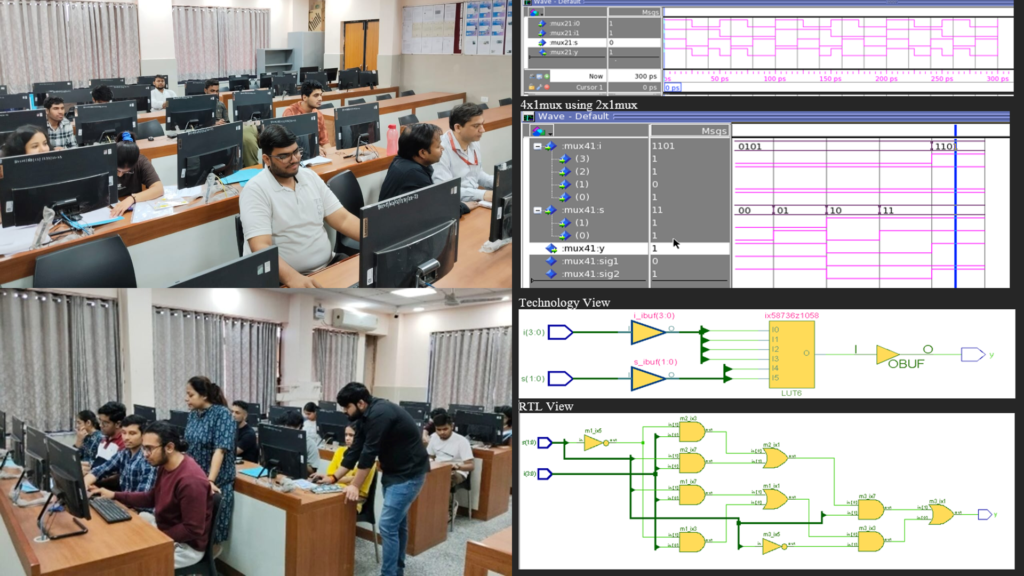

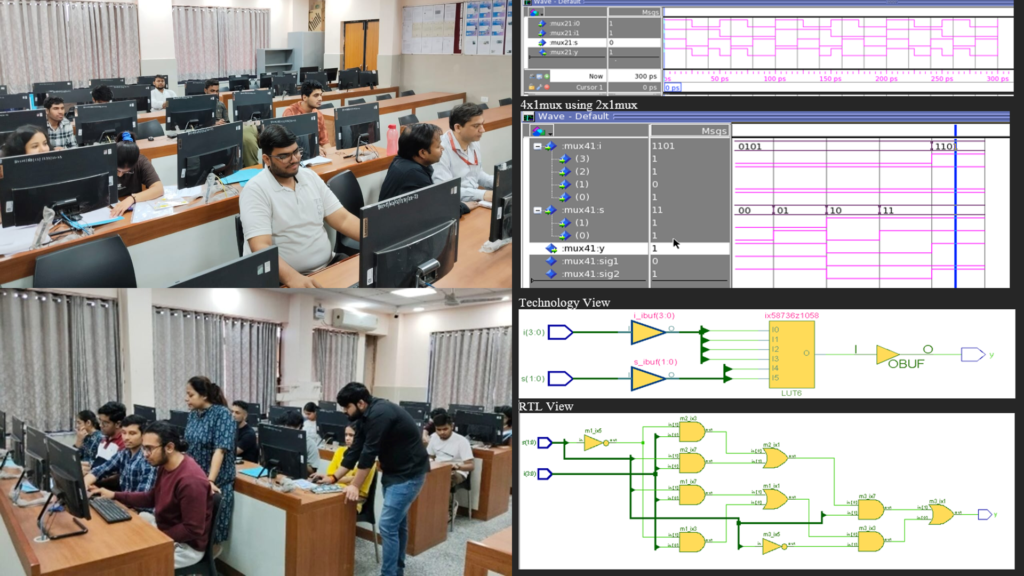

VHDL PROGRAMMING LAB

Introduction

The VHDL Programming Lab is designed to provide students with hands-on experience in digital circuit design using VHDL (VHSIC Hardware Description Language). This lab serves as a foundation for understanding hardware modeling, simulation, and synthesis of digital circuits. Students will explore the implementation of combinational and sequential logic circuits, both synchronous and asynchronous, through simulation and practical applications. By working with industry-standard tools, students will gain essential skills for hardware description, verification, and FPGA-based design, preparing them for careers in VLSI design and digital hardware development.

Course Objectives

| COB-1 |

To provide knowledge of basics of VHDL Programming |

| COB-2 |

To impart knowledge of Combinational logic circuit simulation and its implementation. |

| COB-3 |

To impart knowledge of simulation and implementation of Synchronous Sequential logic circuit. |

| COB-4 |

To impart knowledge of simulation and implementation of Asynchronous Sequential logic circuit. |

Course Outcomes

| CO |

Statement |

Bloom’s Level |

| ECE306T.1 |

Understand the basics of VHDL Programming and its constituents |

Understand, Remember |

| ECE306T.2 |

Implement and analyze the functionality of Combinational logic circuit |

Apply, Analyze |

| ECE306T.3 |

Design and evaluate implementation of Synchronous Sequential logic circuit |

Evaluate, Create |

| ECE306T.4 |

Design Asynchronous Sequential logic circuit and understanding of programable devices |

Create, Understand |

CO-PO-PSO Mapping

| CO/PO |

PO1 |

PO2 |

PO3 |

PO4 |

PO5 |

PO6 |

PO7 |

PO8 |

PO9 |

PO10 |

PO11 |

PO12 |

PSO1 |

PSO2 |

| ECE306T.1 |

3 |

2 |

|

|

2 |

|

|

|

1 |

1 |

|

2 |

3 |

1 |

| ECE306T.2 |

2 |

3 |

3 |

2 |

2 |

|

|

|

1 |

1 |

|

2 |

3 |

2 |

| ECE306T.3 |

2 |

3 |

3 |

2 |

2 |

|

|

|

1 |

1 |

|

|

2 |

3 |

| ECE306T.4 |

2 |

3 |

3 |

2 |

3 |

|

|

|

1 |

1 |

|

2 |

3 |

3 |

Facilities

Facilities

Operating System / Software

| Sr. No. |

Name |

Version |

| 1. |

Windows |

10 |

| 2. |

Siemens (Mentor Graphics) HEP1-Questa |

2019 |

| 3. |

Vivado |

2019 |

Hardware

| Sr.No. |

Equipment Name |

Specification |

Quantity |

| 1. |

Computer |

Intel Core i9 10 Gen 2.10 GH 32 GB RAM |

1 |

| 2. |

Computer |

Intel Core i5 4 Gen 2.10 GH 16 GB RAM |

2 |

| 3. |

Computer |

Intel Core i7 8 Gen 3.10 GH 8 GB RAM |

2 |

| 4. |

Computer |

Intel Core i5 10 Gen 2.10 GH 8 GB RAM |

27 |

| 5. |

Printer |

HP Laser Jet Pro P1108 Plus |

01 |

Staff

- Lab Incharge: Dr. Manoj Sharma

- Other Faculty Members: Dr. Yogita Arora and Dr. Jyoti Gupta

- Lab Assistant: Mr. Deepanshu

Facilities

Facilities